# FABRICATION and CHARACTERIZATION of LOW-NOISE CRYOGENIC Si JFETs

R. T. Goldberg<sup>a</sup> and M. D. Jhabvala

Solid State Device Development Branch, NASA Goddard Space Flight Center

Greenbelt, Maryland 20771

R. K. Kirschman, Suwen Wang, D.-H. Gwo and J. A. Lipa Hansen Experimental Physics Laboratory, Stanford University Stanford, California 94305.

We have custom made Si JFETs with the intent of realizing good low-frequency noise at temperatures in the liquid-nitrogen and liquid-argon range—where the noise of commercial JFETs has typically risen to undesirable levels. We report initial results from the first fabrication lots and for measurements in several circuit configurations, yielding noise voltage levels as low as  $\approx 10-20$  nV/Hz<sup>1/2</sup> at 1 Hz for a 12  $\mu$ m x 2500  $\mu$ m gate JFET ( $K_f \approx 10 \cdot \mu V^2 \cdot \mu m^2$ ).

There are a number of situations where it is useful to operate a low-noise transistor in a cryogenic environment. For applications that demand the lowest possible noise at low frequencies ( $\leq 10$  kHz) where "Iff" noise is usually a problem, the device of choice is the Si JFET, even though its operation is limited to temperatures above  $\approx 40$  K. Other common semiconductor devices, the Si MOSFET and the GaAs MESFET, can operate over the entire cryogenic range, but they cannot yet match the extremely low noise levels of the Si JFET (1).

A number of Si JFETs are commercially available; however, as illustrated by reports since the 1960s, to obtain the lowest possible noise, commercial Si JFETs must usually be operated in the temperature range 100-200 K (2-17). Even though Si JFETs are above their "freeze-out" temperature and can function in the 50-100 K range, obtaining low

<sup>&</sup>lt;sup>a</sup>Hughes STX Corporation, Greenbelt, Maryland.

<sup>&</sup>lt;sup>b</sup>Consulting Physicist, Mountain View, California.

noise in this range is difficult: their noise is significantly increased, sometimes exceeding that at room temperature, although there are exceptions. Also the cryogenic noise level often varies considerably among individual devices of the same type, requiring selection.

Commercial Si JFETs were considered for the low-temperature detector preamplifiers for the X-Ray Spectrometer (XRS) instrument which is slated to fly aboard the Japanese X-ray telescope Astro-E, as well as for readout of the cryogenic star-tracking telescope of the US satellite Gravity Probe B (GP-B) (18-20). The XRS required a noise voltage of <10 nV/Hz<sup>1/2</sup> in the frequency range 10 to 100 Hz at temperatures of 70 to 80 K; whereas for the GP-B telescope, a lower operating temperature is desirable and a somewhat higher noise level would be acceptable in exchange for lower input capacitance. We made low-frequency noise measurements on commercial Si JFETs of recent manufacture, including the Sony 2SK152, the InterFET NJ14AL and NJ30, and the Siliconix U440 (NNZ1 die), but in accord with the earlier reports, they showed noise levels higher than mission specifications in the required temperature ranges. Another drawback is that only certain gate sizes (and thus capacitances) are available.

Moreover, commercial Si JFETs are not designed with cryogenic applications in mind, and their fabrication may be discontinued, modified or transferred to other organizations, with potentially disastrous consequences to their cryogenic characteristics.

It would be extremely useful to have Si JFETs with input capacitance tailored to an application, and that dependably exhibit low noise below 100 K for applications requiring liquid-nitrogen (77 K) or liquid-argon temperature (87 K) operation. Furthermore, for other applications that require coupling the transistor to sensors operating at liquid-helium temperatures or down to the milli-Kelvin range, it would be useful to operate Si JFETs at the lowest possible temperature—at their operating limit of  $\approx 40-50$  K—to minimize power dissipation and heat input to the lower-temperature region of the sensor. The GP-B telescope is one such application, in which the JFETs are the active device for photodiode readout circuits that operate in an  $\approx 2$  K environment (20).

The difficulties of identifying and obtaining Si JFETs with suitable characteristics from commercial sources motivated us to undertake development and characterization of custom Si JFETs specially designed and fabricated for the liquid-nitrogen/liquid-argon temperature range. We describe the design and fabrication of these custom cryogenic Si JFETs, and report initial results from evaluations specifically directed toward their use in photodetector readout circuits for the GP-B telescope.

# I. JFET DESIGN & FABRICATION

Analysis of the noise spectra from our measurements of commercial Si JFETs as a function of temperature over the range 70 to 130 K revealed an electron trap at  $\sim 0.17$  eV below the conduction band with a cross section of  $1 \times 10^{-14}$  cm<sup>2</sup>. Examination of the literature indicated that the trap was possibly due to what is classically referred to as an "A centre" (21). The "A centre" has been studied extensively and is basically an oxygen

replacement of vacancies in the Si lattice. Further examination of the literature (most notably reference 22) led us to assume that these "A centre" defects probably formed during any high-temperature processing of the device. Classical methods of JFET processing involve a high-temperature (up to 1200°C) and long duration (several hours) P+ boron drive-in for conduction channel definition and device isolation. We decided to eliminate this P+ diffusion, as described below.

The basic fabrication of these cryogenic Si n-channel JFETs begins with P+ (boron  $1 \times 10^{19} \text{ cm}^{-3}$ ) (100) silicon wafers, 0.5 mm thick. On these wafers a high-quality 3 µm-thick epitaxial layer of N-type Si is grown (phosphorus  $1 \times 10^{16} \text{ cm}^{-3}$ ) (23). Note that this doping concentration is similar to that used for standard JFETs. The next fabrication step, and possibly the key to low noise, is an anisotropic etching of a channel-stop trench through the N-type epi into the substrate. This trench is etched approximately 4.5 µm deep using KOH solution, and has sloped side walls due to the anisotropy of the etching. By using this "trench" type mesa etching for device isolation rather than the traditional long-time/high-temperature P+ diffusion, we believe damage and defect formation are minimized.

The remaining processing steps are conventional: a P+ (boron) top gate diffusion and an N+ (phosphorus) source/drain ohmic contact diffusion. There are no implants for either of these steps, thus implant damage and annealing are avoided; this is another possible reason for good low-noise performance. The final step is an aluminum deposition for contacts and bond pads, followed by patterning and sintering. The JFET die were not metallized on the backside.

These cryogenic JFETs were designed with a range gate geometries: gate length from 2.5 to 12  $\mu$ m, and gate width from 560 to 3250  $\mu$ m.

## II. MEASUREMENTS & RESULTS

The following types of measurements were made:

- (a) A limited evaluation of basic dc characteristics,

- (b) Noise of individual JFETs,

- (c) Gain and noise in various configurations of the readout circuit, although not operating in readout mode,

- (d) Photon noise (photocurrent shot noise) and JFET noise during operation of the readout circuits in readout mode.

<sup>&</sup>lt;sup>C</sup>We use the conventional nomenclature: gate length is the gate dimension parallel to the channel current and gate width is the gate dimension perpendicular to the channel current. In this paper gate size is always given as length x width.

Measurement methods and results for each of the above types of measurements are described below. Except for readout circuit T-4, as explained below, all individual FET: or circuits were assembled onto TO-5 headers. In all cases the JFET die were attached with silver epoxy; high-temperature eutectic die attach was avoided. For the cryogenic measurements the entire circuit (including the semiconductor die) was exposed and was immersed directly into liquid nitrogen. Even for the floating-gate noise measurements this direct immersion was practical, and measurements made with the circuits in the cold nitrogen gas above the liquid resulted in the same, or in some cases worse, noise. However, microphonics could be a problem, so it was necessary to avoid vibration or disturbances. The measurements were made with low power dissipation  $(-10-100 \ \mu\text{W})$ , in accord with the requirements for the GP-B readout. All noise spectra and figures of merit given in (b) and (c) below, are of noise voltage and are gate-referred (1).

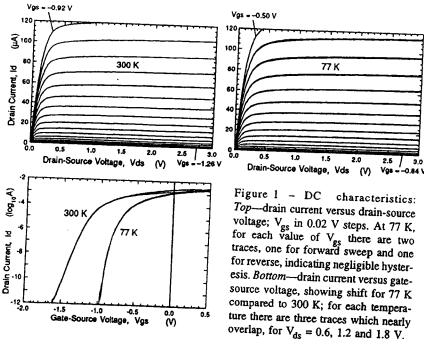

(a) DC Characteristics DC characteristics were made using a Hewlett Packard 4145A Semiconductor Parameter Analyzer. The custom cryogenic JFETs exhibited excellent dc characteristics at liquid-nitrogen temperature, with the usual shift towards positive gate bias (towards zero) compared to room temperature, as shown in Figure 1 for a 12 µm x 2500 µm JFET.

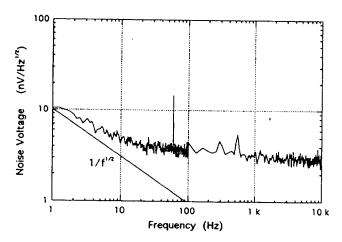

(b) Noise of Individual JFETs An example of the liquid-nitrogen shorted-gate noise-voltage spectrum for an individual 12  $\mu m \times 2500~\mu m$  JFET (Figure 2) illustrates the excellent noise level, with  $K_f \equiv A_f \times gate$  area  $\approx 8~\mu V^2 \cdot \mu m^2$  (1) for a power dissipation of only 60  $\mu W$  in the JFET.

Figure 2 – Shorted-gate, gate-referred noise-voltage spectrum for a 12  $\mu$ m x 2500  $\mu$ m gate custom cryogenic Si JFET at 77 K;  $I_d$  = 50  $\mu$ A,  $V_{ds}$  = 1.2 V ( $g_m$  = 0.6 mS).

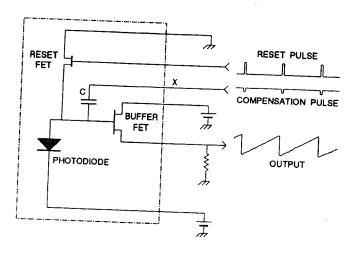

(c) Gain and Noise of JFETs in Readout-Circuit Configuration The photodiode readout circuit used for these evaluations is shown in Figure 3, in which a custom Si JFET is used as the buffer FET. During operation the photodiode current is integrated on the combined capacitance of the photodiode, buffer JFET gate, reset FET, compensation capacitor C and any stray capacitance. As the charge accumulates, a voltage ramp is output, with slope proportional to the photocurrent, I<sub>p</sub>.

However, for the measurements described in this section this circuit was not operated in readout mode. First, shorted-gate noise measurements were made on the buffer JFET using direct connections; to access the gate a temporary bond wire shorted the compensation capacitor, C. The gain and noise were measured by using two different circuits: (1) grounded source, with V<sub>ds</sub> fixed, as described in reference (24), and (2) source-follower. Subsequently, the temporary bond wire was removed to allow the JFET gate to "float", and the gain and noise measurements were repeated at liquid-nitrogen

Figure 3 — Basic readout circuit being evaluated in these measurements. The portion within the dashed line operates at cryogenic temperature.

temperature only. In both cases a test signal was fed into point "X" for the gain measurements, and point "X" was grounded for the noise measurements. The reset FET was turned off for all these measurements. Circuit operation in the floating-gate mode was verified by using the photodiode as an isolated current source, and repeating the measurements after integrating charge onto the JFET gate by momentarily illuminating the photodiode. Comparison of the gains between the shorted-gate and floating-gate measurements allowed an estimate of the circuit capacitance as well as the JFET gate-to-source capacitance, since the capacitance of C was known (3 to 7 pF, depending on the circuit).

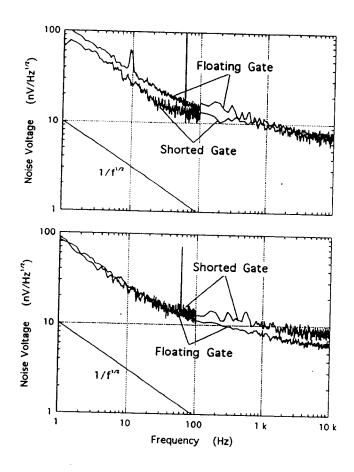

Such measurements were made on three readout circuits having different size JFETs. The noise-voltage spectra for readout circuit NB-1 having the smallest JFET (5  $\mu m$  x 560  $\mu m$ ) are shown in Figure 4. For all measurements the JFET power dissipation was approximately 16  $\mu W$  (V<sub>ds</sub> = 1.2 V, I<sub>d</sub> = 13  $\mu A$ , g<sub>m</sub> = 0.24 mS) and V<sub>gs</sub> was approximately 1 V. Figure 4 shows good agreement among the spectra for the various circuit configurations; the source-follower floating gate spectrum has been divided by the appropriate input capacitance ratio, (C<sub>gs</sub> + C<sub>total</sub>)/C<sub>total</sub> = 2.0 for this circuit, where C<sub>gs</sub> is the buffer FET gate-to-source capacitance and C<sub>total</sub> is the total input capacitance. Similar results (but with lower noise) were obtained for the other two circuits, having larger JFETs.

Figure 4 - Noise-voltage spectra at 77 K for a 5 μm x 560 μm gate Si JFET in a readout circuit (Figure 3): *Top*—for grounded-source measurement circuit. *Bottom*—for source-follower measurement circuit. All four noise spectra are in good agreement.

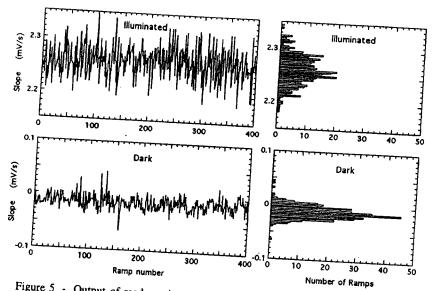

(d) Noise during Readout Operation of Readout Circuits The output voltage ramps from two readout circuits were collected during readout operation at cryogenic temperature under conditions approximating the projected operating conditions for the GP-B telescope. Both circuits used the 5 μm x 560 μm gate JFET. The circuits were operated inside a vacuum can during the measurements: for circuit NB-1 (the same circuit described in (c) above), built directly on a TO-5 header, the vacuum can was immersed in liquid nitrogen; whereas for circuit T-4, built on a thermal isolation platform and heated with a power of approximately 200 μW (~40 μW in the FET, the remainder in a heater resistor), the vacuum can was immersed in liquid helium (25). The results for circuit NB-1, with and without illumination on the photodiode, are shown in Figure 5; the left-hand plots are the slopes of 400 successive integration ramps output by the readout circuit, and the right-hand plots are histograms of the distribution of the 400 slopes.

Figure 5 - Output of readout circuit NB-1 operating at 77 K with 0.1 seconds between resets: *Top*—with illumination generating ≈15 fA photocurrent, showing photon (shot) plus preamplifier noise. *Bottom*—without illumination, showing preamplifier (JFET) noise only. Slopes of the output ramps are plotted on the left and corresponding histograms of the distribution of the slopes are on the right.

<sup>&</sup>lt;sup>d</sup>The readout circuit outputs were passed through a 1 kHz filter and then sampled at 4 kHz; the slope of each ramp was determined as a least squares fit to 320 sampled points along the ramp.

Standard deviations derived from the data plotted in Figure 5 for photon (shot) noise (subtracting the JFET noise, right-most column in Table 1) are in reasonable agreement with those calculated from shot-effect statistics (column 4),  $\Delta I_p = (eI_p/\Delta t)^{1/2}$ . An integration capacitance,  $C_i$ , of ~6.5 pF determined as described in section (c) is used to calculate the photocurrent,  $I_p = C_i x$  slope. Also, the JFET noise is comparable to the photon noise for both circuits. The photodetector is assumed to be noiseless at the cryogenic temperatures.

Table 1 - Readout circuit characteristics: second column is the average slope of the 400 ramps as plotted is Figure 5 (illuminated); the corresponding average photocurrent is given in column 3; columns 4 and above are standard deviations given in mV/s and in fA.

| Readout<br>circuit | Average<br>slope<br>(mV/s) | Average<br>photocurrent,<br>i <sub>p</sub> (IA) | Calculated shot noise | Total measured<br>noise<br>(illuminated) | Measured<br>JFET noise<br>(dark) | Net measured<br>shot noise |

|--------------------|----------------------------|-------------------------------------------------|-----------------------|------------------------------------------|----------------------------------|----------------------------|

| NB-1               | 2.26                       | 15                                              | 0.024/0.16            | 0.028/0.18                               | 0.0115/0.075                     | 0.026/0.17                 |

| T-4                | 1.15                       | 7.5                                             | 0.017/0.11            | 0.017/0.11                               | 0.0084/0.055                     | 0.015/0.098                |

#### III. SUMMARY/CONCLUSIONS

By means of custom fabrication, we have made Si JFETs that exhibit excellent low-frequency noise at temperatures for which the noise of commercial JFETs has typically risen to undesirable levels. These custom JFETs are thus suited for applications where it is desirable that circuits operate at temperatures in the liquid-nitrogen/liquid-argon range, or at as low a temperature as possible, down to the operating limit of Si JFETs. We attribute their cryogenic performance to special attention to design and fabrication procedures. The JFETs were evaluated for use in readout circuits for photodiodes for the Gravity Probe B telescope, but the results are applicable to other applications.

These cryogenic JFETs were found to exhibit  $K_f$  values at 77 K between  $\approx 8$  and  $\approx 20$   $\mu V^2 \cdot \mu m^2$  at low drain current ( $\approx 10-50$   $\mu A$ ). This compares favorably with recent reports of measurements near this temperature for commercial Si JFETs giving  $K_f \approx 25$  and  $\approx 140$   $\mu V^2 \cdot \mu m^2$  (16,17). Also we found that floating-input noise corresponded to shorted-input noise, thus gate-referred noise current was not measurable, as expected.

The measurements of most interest for the GP-B telescope are those of readout circuits, and the noise values for different circuits and measurement configurations agree with one another as predicted from analysis of the circuits and values of capacitance calculated from gain measurements.

## IV. ACKNOWLEDGEMENTS

We thank S. Wong and J. Shott and the Center for Integrated Systems (Stanford Univ.) for continued technical support with device characterization, and for custom fabrication of Si MOS reset FETs; we also thank L. Rhen (InterFET) for helpful discussions on JFET technology, and E. Low (Infrared Labs.) for support with readout development P. Prather and the Ginzton Lab. (Stanford Univ.) provided technical support and W. Smith, R. Sheasley, A. Jung and J. Hardin (Hewlett Packard) made vital contributions to data conversion and analysis. We appreciate review of this paper by N. Madden (Lawrence Berkeley Lab.) and V. Radeka (Brookhaven National Lab.).

The part of this work performed at Stanford (GP-B) was supported by NASA under Contract NAS8-36125 out of Marshall Space Flight Center.

#### V. REFERENCES

- 1. R. K. Kirschman, "Transistor noise characteristics for low-frequency analog cryogenic instrumentation" *Proceedings of the Symposium on Low Temperature Electronics and High Temperature Superconductivity*, eds. S. I. Raider, C. Claeys, D. P. Foty, T. Kawai and R. K. Kirschman, The Electrochemical Society, 1993, Proceedings vol. 93-22, pp. 223-235.

- 2. T. V. Blalock, "Wide-band low-noise charge sensitive preamplifier" *IEEE Trans. Nuclear Science*, v. NS-13, n. 3, June 1966, pp 457-467.

- 3. K. F. Smith and J. E. Cline, "A low-noise charge sensitive preamplifier for semiconductor detectors using paralleled field-effect-transistors" *IEEE Trans. Nuclear Science*, v. NS-13, n. 3, June 1966, pp 468-476.

- 4. E. Elad and M. Nakamura, "High-resolution beta- and gamma-ray spectrometer" *IEEE Trans. Nuclear Science*, v. NS-14, n. 1, 1967, pp 523-531.

- 5. V. Radeka, "Field-effect transistor noise as a function of temperature and frequency" Gatlinburg Conference on Semiconductor Radiation Detectors and Circuits, 15-18 May 1967, pp. 24.

- 6. R. A. Spaulding, "Field-effect transistor noise at low temperatures" *Proceedings of the IEEE*, v. 56, n. 5, pp. 886-887, May 1968.

- 7. P. T. Anderson, B. Bertman and R. R. Wagner, "Low level signal amplifiers at cryogenic temperatures" Refrigeration Science and Technology; Cryophysics and Cryoengineering Commission, International Institute of Refrigeration, 1970, pp 211-214.

- 8. F. M. Klaassen and J. R. Robinson, "Anomalous noise behavior of the junction-gate field-effect transistor at low temperatures" *IEEE Trans. on Electron Devices*, v. ED-17, n. 10, pp. 852-857, Oct. 1970.

- 9. M. J. Churchill and P. O. Lauritzen, "Carrier density fluctuation noise in silicon junction field effect transistors at low temperatures" *Solid-State Electronics*, v. 14, pp. 985-993, 1971.

- 10. J. W. Haslett and E. J. M. Kendall, "Temperature dependence of low-frequency excess noise in junction-gate FETs" *IEEE Trans. on Elect. Dev.*, v. ED-19, n. 8, p. 943-950, Aug. 1972.

- 11. J. W. Haslett, E. J. M. Kendall and F. J. Scholz, "Design considerations for improving low-temperature noise performance of silicon JETs" *Solid-State Electronics*, v. 18, n. 2, pp. 199-207, Feb. 1975.

- 12. P. D. LeVan, "Preamplifier noise in indium antimonide detector systems" SPIE (Society of Photo-Optical Instrumentation Engineers), v. 246, 1980, pp. 34-38.

- 13. F. Bordoni, G. Maggi, A. Ottaviano and G. V. Pallottino, "Very low noise cooled audiofrequency preamplifier for gravitational research" *Review, of Scientific Instruments*, v. 52, n. 7, July 1981, pp 1079-1086.

- 14. G. H. Rieke, E. F. Montgomery, M. J. Lebofsky and P. R. Eisenhardt, "High sensitivity operation of discrete solid state detectors at 4 K" Applied Optics, v. 20, n. 5, 1 March 1981, pp 814-818.

- 15. F. Ayela, J. L. Bret and J. Chaussy, "Noise measurements on silicon J-FETs at low temperature using a very high Q superconducting resonator" *Review of Scientific Instruments*, v. 62, n. 11, Nov. 1991, pp. 2816-2821.

- 16. N. W. Madden, F. S. Goulding, J. M. Jaklevic, D. A. Landis, C. S. Rossington and J. T. Walton, "An improved operating mode for a Si(Li) X-ray spectrometer" *IEEE Nuclear Science Symposium* 15-19 Jan. 1990, San Francisco, California; *Lawrence Berkeley Laboratory Report LBL-27067*.

- 17. L. Lanzi, K. Sassoli and G. Ventura, "NJ3600L FET as a very low-noise, cooled amplifier for infrared bolometry" *Cryogenics*, v. 34, n. 11, Nov. 1994, pp. 959-960.

- 18. C. W. F. Everitt, "Gravity Probe B: I. The Scientific Implications" Proc. Sixth Marcel Grossmann Meeting on Relativity, 23-29 June 1991, Kyoto, Japan.

- 19. D. Bardas et al., "Gravity Probe B: II. Hardware Development; Progress towards the Flight Instrument" Proc. Sixth Marcel Grossmann Meeting on Relativity, 23-29 June 1991, Kyoto, Japan.

- 20. J. A. Lipa, D.-H. Gwo and R. K. Kirschman, "Status of the cryogenic inertial reference system for the Gravity Probe B mission" SPIE Proceedings, v. 1765, Cryogenic Optical Systems and Instruments V, 1992, pp. 85-93.

- 21. S. D. Brotherton and P. Bradley, "Defect production and lifetime control in electron and γ-irradiated silicon" *Journal of Applied Physics*, v. 53, n. 8, pp. 5720-5732, Aug. 1982.

- 22. F. Shimura, Semiconductor Silicon Crystal Technology Academic Press, 1989; chapter 7, pp. 279-344.

- 23. Epitaxy by Hughes Technology Center, Carlsbad, California.

- 24. R. K. Kirschman, S. V. Lemoff and J. A. Lipa, "Evaluation of GaAs FETs for cryogenic readout" *Infrared Readout Electronics*, 21-22 April 1992, Orlando, Florida, SPIE (Society of Photo-Optical Instrumentation Engineers) Proceedings vol. 1684, ed. E. R. Fossum, 1992, pp.110-130.

- 25. The mechanical and thermal design for readout T-4 was adapted from a design by Infrared Laboratories, Tucson, Arizona.